The A510 is 50% wider than its predecessor, the Cortex-A55 which was 2-wide.Įach cycle, up to three μOPs may be sent to execution. To match fetch and decode width, the A510 features a 3-wide issue and execute.

Because the effective utilization of the vector unit on the small cores is quite low, by implementing a single vector unit for two A510 cores, the silicon area is maintained relatively low while still offering good peak performance when needed.Įach cycle, up to three instructions are decoded and sent to the back-end for execution. The only difference is that you are dealing with two cores at once in a single instance. Like any other Arm IP, the Cortex-A510 complex can be instantiated within a standard DSU cluster as any other core would. A core complex tightly integrates two Cortex-A510 cores, sharing a single common level 2 cache and vector processing unit (VPU). The Cortex-A510 introduces the concept of a Core Complex along with a merged core architecture. The Cortex-A510 is the first small core from Arm to feature the Armv9 ISA along with the Scalable Vector Extension (SVE) and SVE2 extensions. However, by borrowing high-performance components such as state-of-the-art branch predictors and prefetchers, the Cortex-A510 enjoys significantly higher performance over its predecessor through higher effective instruction stream throughput. To maintain high efficiency, the Cortex-A510 remains an in-order architecture. Designed to be ultra-low-power and versatile, this core can be used as a standalone CPU in low-power SoCs or serve the efficient core as part of a DynamIQ big.LITTLE architecture using the DSU-110. The Cortex-A510 is Arm's successor to the Cortex-A55 which was introduced four years earlier.

#Cache coherence cortex a9 code

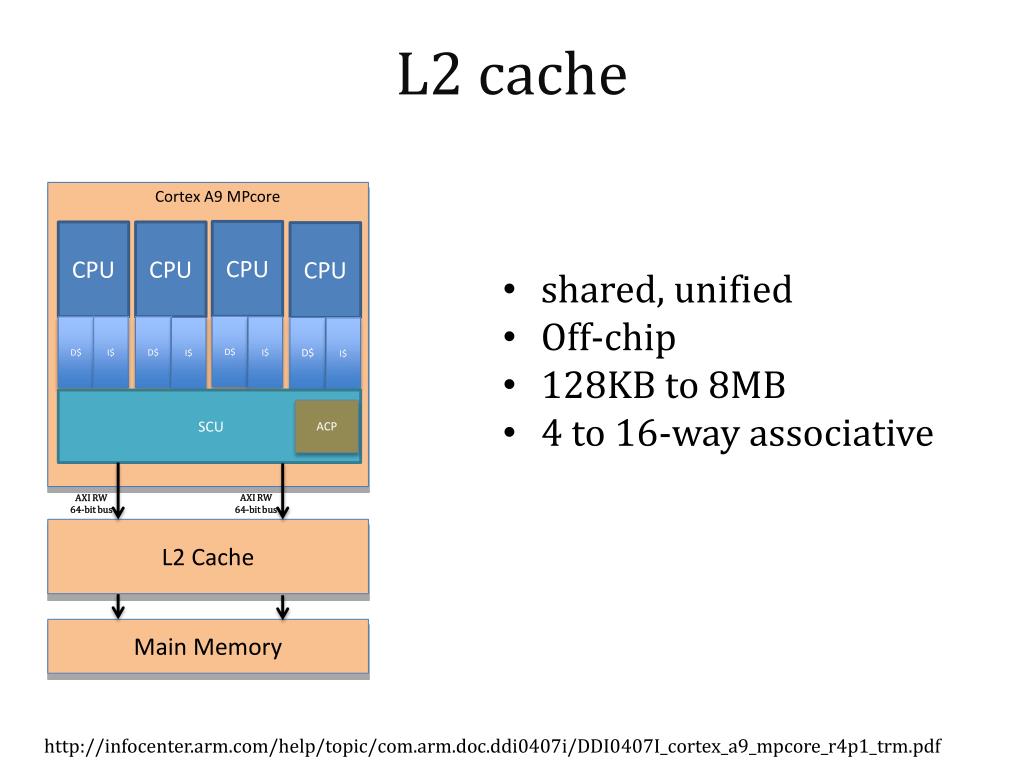

Error Correcting Code (ECC) cache protection.Virtually-Indexed, Physically-Tagged (VIPT) behaving as Physically-Indexed, Physically-Tagged (PIPT).

Single Error Detect (SED) parity cache protection.Virtually-indexed, physically-tagged (VIPT) behaving as physically-indexed, physically-tagged (PIPT).32 KiB OR 64 KiB, 4-way set associative.The Cortex-A510 has a private L1I, L1D, and cluster-wide L2 cache. 2x loads (2 lds/cycle, up from 1/cycle)īlock Diagram Core Complex Memory Hierarchy.Wider loads (128b/cycle, up from 64b/cycle).Core Complex with a merged core architecture.Lower power (Arm claims: -20% energy iso-performance / +10% performance iso-power).Higher performance (Arm claims: +35% IPC (SPECint 2006) / +50% IPC (SPECfp 2006).The Cortex-A510 is also designed to seamlessly integrate along with higher-performance cores through Arm's DynamIQ big.LITTLE technology. It borrows advanced processor components from Arm's high-performance cores - such as the branch prediction and prefetchers - to extract high performance from a traditional in-order core design. The Cortex-A510 is a brand new ground-up CPU design. The Cortex-A510 was primarily designed to take advantage of TSMC's 7 nm, 6 nm, 5 nm as well as Samsung's 7 nm and 5 nm.

0 kommentar(er)

0 kommentar(er)